|

Zu Beginn des FPGA Design Pfads im System Designer wird eine HDL (Hardware Description Language) Beschreibung des FPGA erwartet. Sowohl Verilog als auch VHDL ist möglich. Man kann diese Datei entweder von Hand erstellen, oder mit einem grafischen Codegenerator wie dem im Paket enthaltenen ,,HDL Planner`` erzeugen.

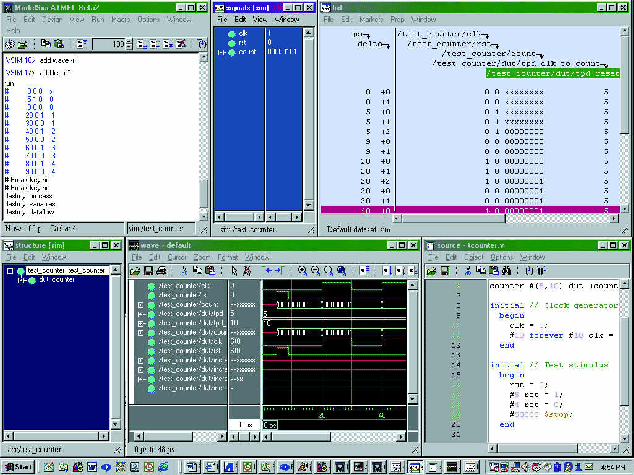

Sobald die Beschreibung des FPGA fertig ist geht es weiter zum nächsten Schritt: der funktionalen Simulation. Hier kommt ModelSim von Mentor Graphics zum Einsatz. (Abbildung 5) Für die Simulation wird eine ,,Testbench`` benötigt. Das ist eine vom Entwickler zu erstellende Datei, die dazu verwendet wird, Eingaben für den zu testenden Hardware-Entwurf zu erzeugen. Die Simulation ist immer nur so gut, wie die verwendeten Testdaten.

Dieser Schritt ist optional und kann auch dann durchgeführt werden, wenn die FPGA Entwicklung unabhängig von der AVR-Entwicklung erfolgt. Hier wird nur das FPGA getestet.

Bisher besteht eine allgemeingültige Beschreibung der des logischen Aufbaus der Schaltung. Um diese jetzt auf die in der Hardware vorhandenen Gates auf dem FPGA anzupassen bedarf es der HDL Synthese. In diesem Schritt wird das Design analysiert und auf die Zielhardware angepasst. Das Programm ,,LeonardoSpectrum`` (Abbildung 6) ist für das erstellen der Netzlistendatei zuständig.

Diese Netzliste wird im nächsten Schritt, ,,FPGA Place & Route`` in das Programm ,,Figaro`` importiert. Figaro ist für die Platzierung der Schaltung in den einzelnen Gates und den Entwurf der Verbindung verantwortlich. Mittels der Netzliste bestimmt Figaro die für das Design benötigten Zellen. Platzierung und Verbindung ist ähnlich wie beim Entwurf von Leiterplatinen. Zunächst werden Zellen unabhängig von den Verbindungen ausgewählt. Dann werden sie verschoben, bis die benötigten Verbindungen möglich sind. Je nach Komplexität des Designs und gewünschter Optimierung ist dieser Vorgang sehr rechenintensiv. Der Prozess läuft automatisch ab, es ist aber möglich das Ergebnis von Hand zu optimieren. Das Ergebnis wird als Schaltplan wie in Abbildung 7 angezeigt. Figaro erzeugt die zur Programmierung der Hardware nötige Bitstream Datei.

Besonders wenn von Hand Verbesserungen vorgenommen wurden bietet sich der optionale letzte Schritt im FPGA-Entwurfsablauf an: die Postlayout Simulation. Hiermit kann überprüft werden, ob sich das fertige Design immer noch so verhält wie es soll.