|

Der verwendete Mikrocontrollerkern ist ein AVR 8-Bit RISC. Er wird mit einer Taktrate von 25 MHz betrieben. AVR ist ein Standard Mikrocontroller, der ebenfalls zu Atmels Produktpalette gehört. Als Einzelbauteil ist dieser Mikrocontroller weit verbreitet und wird gerne z.B. im Automobilbereich verwendet.

Die embedded Variante erreicht etwa 1Mips/MHz. Da die meisten Maschinenbefehle innerhalb eines Taktes ausgeführt werden erreicht der AVR auf dem FPSLIC mit seinen 25MHz bis zu 25 MIPS, im Normalbetrieb etwa 20 MIPS. (Million Instructions Per Second)

Der AVR-Kern ist ein Niedrigenergie CMOS 8-Bit Mikrocontroller der auf der AVR RISC Architektur basiert. Diese erweiterte RISC Architektur verfügt über 32 8Bit Register. All diese Register sind direkt mit der ALU (Arithmetic Logic Unit) verbunden so daß mit einer einzigen Anweisung auf zwei unabhängige Register zugegriffen werden kann. Diese Anweisung wird innerhalb eines Taktes ausgeführt. Diese Architektur erzielt einen bis zu 10 Mal höheren Befehlsdurchsatz als ein CISC (Complex Instruction Set Computing, Sammelbezeichnung für nicht RISC R=reduced) Mikrocontroller.

AVR verwendet die Harvard Architektur: Programm- und Datenspeicher sind getrennt1 . Der Prozessor hat getrennte Busse für Instruktions- und Datenzugriff. Dadurch ist Parallelverarbeitung möglich. Während eine Anweisung ausgeführt wird kann bereits die Nächste gelesen werden. Dadurch kann in jedem Taktzyklus eine Anweisung ausgeführt werden. Da das bei bedingten Sprüngen nicht funktioniert ist 1 MIPS/MHz die maximal mögliche Leistung, realistisch wird etwa 0.8 MIPS/MHz erreicht

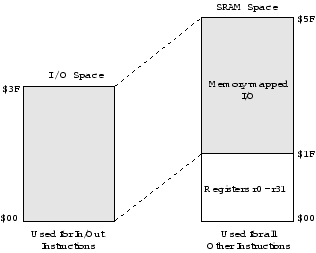

Die Register werden in den Speicher abgebildet. Jedes Register hat eine Adresse im Datenbereich. Genauso ist der I/O Bereich ,,Memory Mapped`` wie in Abbildung 2 dargestellt. Die I/O Ports sind mit der Peripherie verbunden.