|

Bis jetzt haben wir die Entwicklung für AVR und FPGA getrennt betrachtet. Um aber wirklich einen Vorteil vom System on a Chip zu haben müssen

Zuerst sind gerätespezifische Einstellungen vorzunehmen. Normalerweise findet dieser Schritt bereits vor Beginn der übrigen Entwicklung statt. Es muß entschieden werden, wieviel Speicher für Code und wieviel für Daten zur Verfügung steht. Es muß festgelegt werden, mit welchem Takt das FPGA betrieben wird.

Darüber hinaus muß sich der Entwickler klar werden, welche Teile seines Entwurfs in Hardware auf dem FPGA realisiert werden und was als Programm auf dem AVR. Gerade wenn als Team entwickelt wird ist eine genaue Festlegung der Zuständigkeiten nötig.

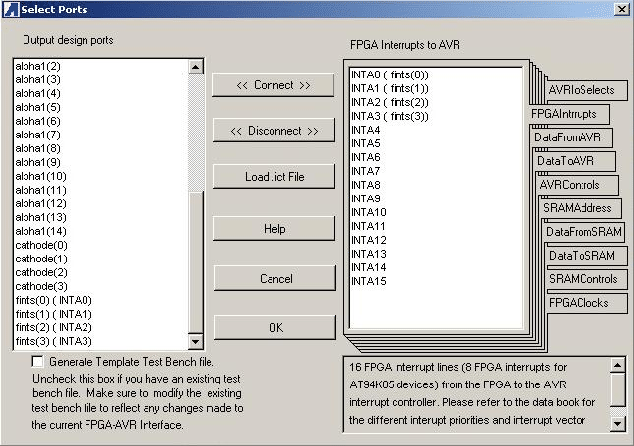

Sobald die HDL Beschreibung des FPGA fertig ist ist können die physikalischen Verbindungen zwischen dem FPGA und dem AVR festgelegt werden. Den Dialog zum Herstellen dieser ,,Interface Connections`` zeigt Abbildung 9. Das linke Feld zeigt die möglichen Anschlüsse am AVR-Kern, rechts stehen die des FPGA. Um ein Paar zu verbinden werden einfach beide mit der Maus ausgewählt und der ,,Connect`` Button gedrückt. Auf Wunsch kann automatisch eine Vorlage für eine entsprechende ,,Testbench`` generiert werden.

Nachdem der AVR-Code fertig ist kann der erste Durchlauf der Co-Verifikation beginnen. Die Co-Verifikation erlaubt es, den fertigen AVR-Code mittels einer Simulation auszuführen. Hierzu wird wieder ModleSim eingesetzt. Das erste Mal berühren sich hier die Entwicklungspfade für FPGA und AVR.

Das FPGA Entwicklerteam kann mit der HDL Synthese weitermachen während die Co-Verifikation läuft. Durch die Parallelisierung dieser Pfade kann Entwicklungszeit eingespart werden. Zumindest solange, bis bei der Co-Verifikation Fehler entdeckt werden.

Sobald das FPGA Entwicklerteam mit Synthese, Layout und Routing fertig ist beginnt der zweite Durchlauf der Co-Verifikation. In diesem zweiten Durchlauf wird eine Simulation unter der Berücksichtigung der Timinginformationen vom FPGA Plazierungs- und Routingprozess durchgeführt. Die Abbildungen 10 und 11 zeigt die gleichzeitige Simulation von AVR und FPGA.

Gewöhnlich wird jetzt auch ein Prototyp der Platine des Geräts, in dem das System on a Chip eingesetzt werden soll, entworfen. Es ist auch möglich, das FPSLIC Starter Kit als frühen Prototyp zu verwenden.