|

Für eine effiziente Zusammenarbeit zwischen dem AVR-Kern und dem FPGA ist die Übertragung von Daten zwischen diesen beiden Komponenten entscheidend. Um dies zu gewährleisten können beide auf das SRAM zugreifen.

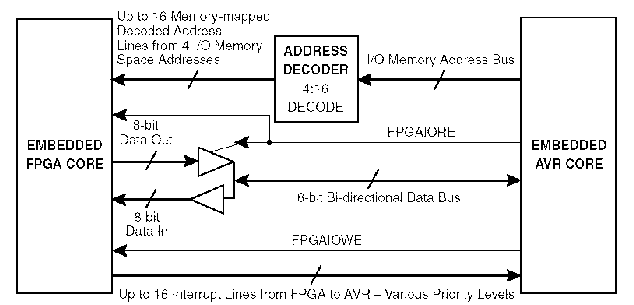

Abbildung 3 zeigt die Verbindungen, die mit dem ,,Interface Connections`` Dialog (siehe 4.3) im System Designer programmiert werden.

Zum einen ist das eine Datenbusverbindung. Das AVR Datenbusinterface ist direkt mit dem Bus des FPGA verbunden, so daß das FPGA als großes I/O Device behandelt wird.

Mittels zu 16 ,,decoded address lines`` können direkt AVR Speicherzugriffe direkt auf Schnittstellen des FPGA gemappt werden.

Das FPGA hat die Möglichkeit Interrupts zum AVR zu schicken. Dabei sind bis zu 16 verschiedene Interrupts möglich.